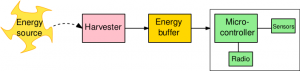

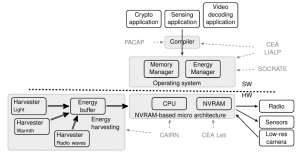

The ZEP project addresses the issue of designing tiny computing objects with no battery by combining non-volatile memory (NVRAM), energy harvesting, micro-architecture innovations, compiler optimizations, and static analysis. The main application target is Internet of Things (IoT) where small communicating objects will be composed of this computing part associated to a low-power wake-up radio system. The ZEP project gathers four INRIA teams that have a scientific background in architecture, compilation, operating system and low power together with the CEA Lialp and Lisan laboratories of CEA LETI & LIST. The major outcomes of the project will be a prototype harvesting board including NVRAM and the design of a new microprocessor associated with its optimizing compiler and operating system.

You can find the initial detailed description of the project here : ZEP-proposal

The scientific work (in progress) is organized around three fields :

- a specific NVRAM-based architecture

- a dedicated compiler pass that computes a worst-case energy consumption

- an operating system managing NVRAM and energy, ensuring memory consistency across power outages

The project is illustrated by the figure below, where PACAP, SOCRATE, CORSE, and CAIRN are the teams involved in the project.

Another important goal of the project is to structure the research and innovation that should occur within INRIA to prepare the important technological shift brought by NVRAM technologies.