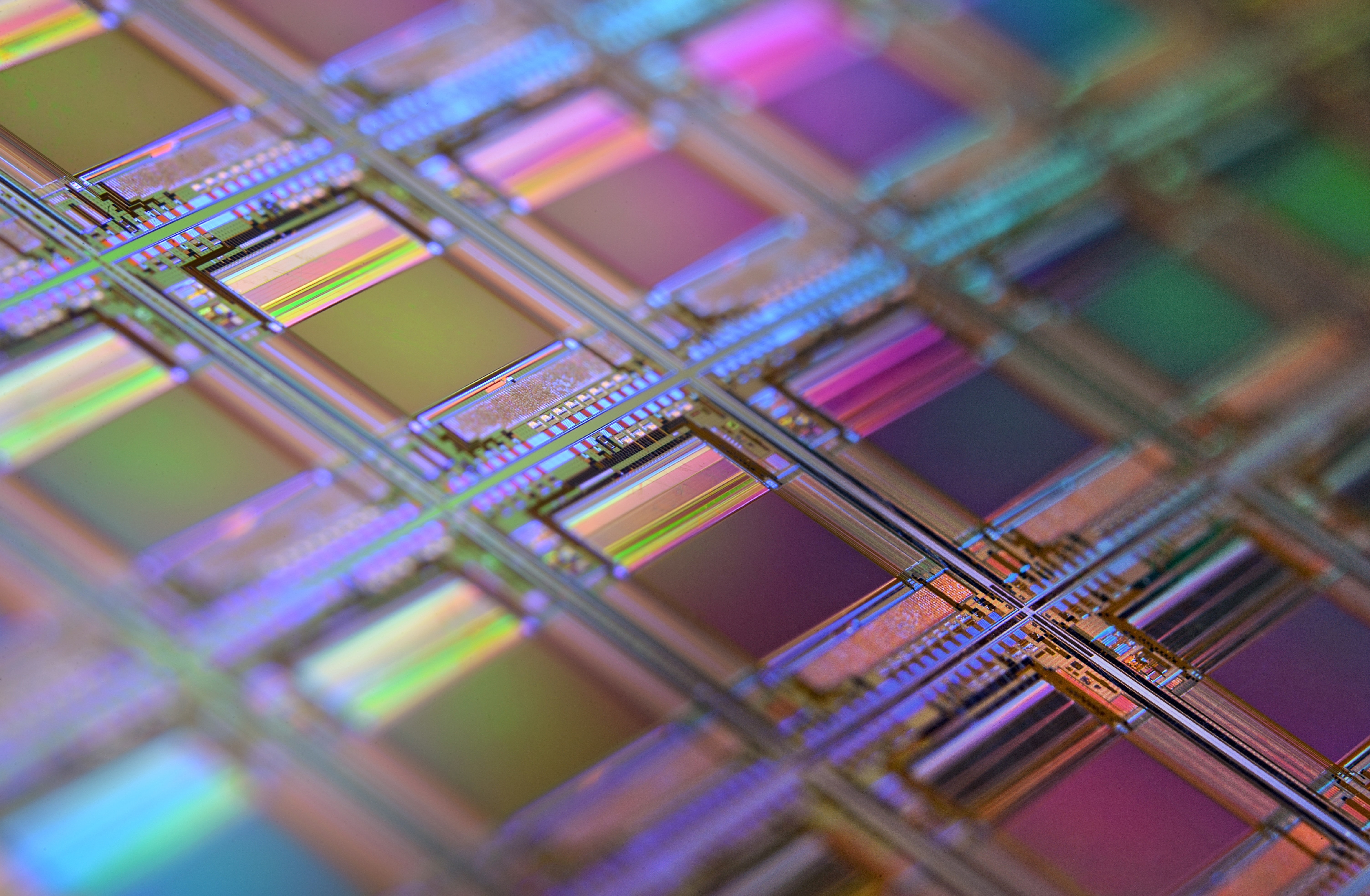

Utilisés pour fabriquer les circuits intégrés, les transistors de la technologie CMOS sont miniaturisés à l’extrême afin que les processeurs puissent en embarquer un maximum et ainsi fournir des performances toujours plus élevées. Mais la place vient à manquer. Arrivée à ses limites, cette technologie ne permet plus de gains d’échelle. D’où le besoin d’un autre paradigme. Nouvelle équipe-projet d’Inria à Rennes et Lannion, Taran prône donc la spécialisation des architectures de calcul.

Énoncée en 1965, la loi de Moore postule que le nombre de transistors sur les puces de microprocesseurs double en gros tous les deux ans, augmentant d’autant la puissance de nos ordinateurs. La prophétie s’est toujours confirmée. Mais depuis quelque temps, elle s’essouffle. Certes, les puces du dernier smartphone embarquent la bagatelle de 16 milliards de transistors dont la largeur de canal n’excède pas les 5 nanomètres. “Mais il n’y a plus vraiment de place pour faire passer des électrons et on pourra difficilement miniaturiser davantage, prévient Olivier Sentieys, responsable de la nouvelle équipe de recherche Taran. Il va donc falloir chercher une alternative du côté de la spécialisation du matériel car, dans le fond, nos machines ne sont pas très efficaces. Elles savent tout faire, mais elles ne le font pas très bien.” Dans leur discours de réception du prix Turing, en juin 2018, les lauréats John Hennessy et David Patterson dressaient d’ailleurs le même constat, annonçant au passage un nouvel âge d’or pour les concepteurs d’architectures.

Dans cette nouvelle ère, « le processeur sera entouré par toute une série d’accélérateurs matériels chargés d’effectuer des tâches spécifiques de façon plus efficace. Le thème central de notre équipe porte sur la conception d’accélérateurs à la fois économes en énergie et tolérants aux erreurs ou aux fautes.”

Élément clé de ces architectures frugales : le calcul au plus juste.

Il s’agit de réduire au maximum le nombre de bits utilisés pour une opération. On réalise ainsi des gains considérables en convertissant par exemple du code 64 bits à virgule flottante en spécification 12 bits (ou moins) à virgule fixe.

Rayons cosmiques

La miniaturisation vers l’échelle nanométrique engendre aussi des problèmes de fiabilité. À cela diverses raisons. En particulier les rayonnements cosmiques qui provoquent parfois des erreurs transitoires sur les très petits transistors. D’où la nécessité de construire des architectures résilientes. “Dans le spatial, par exemple, pour assurer de la redondance, les processeurs sont tripliqués. Si l’un d’eux produit un résultat erroné, on se fie aux deux autres qui continuent d’afficher une valeur correcte. Nous aimerions proposer des architectures à la fois résilientes et frugales. Ce serait quand même mieux de faire de la tolérance aux fautes sans avoir à tripliquer systématiquement tout le hardware.”

Nanotubes de carbone, spintronique, mémoire non volatile

En toile de fond à tout cela s’ajoute l’émergence de plusieurs nouvelles technologies que les chercheurs souhaitent regarder de près. “Le nanotube de carbone ou la spintronique pourrait un jour remplacer le transistor en silicium. De leur côté, les communications photoniques permettraient de transmettre les données d’un accélérateur à l’autre en utilisant la lumière. La mémoire non volatile, quant à elle, conserve les informations même si le matériel n’est pas sous tension. Toutes ces technologies présentent des avantages et des inconvénients. Nous allons étudier des architectures pour tirer parti des premiers sans subir les seconds.”

Lors de travaux précédents, les scientifiques ont conçu deux outils principaux. Un compilateur nommé GeCoS et un environnement pour optimiser la précision des calculs appelé Typex. Ce dernier fait actuellement l’objet d’un transfert de technologie vers Quintech, une jeune entreprise issue d’Inria spécialisée dans l’optimisation pour systèmes embarqués.

Dans les années qui viennent, il faudra aussi de nouveaux langages “Les concepteurs d’accélérateurs doivent s’accommoder de techniques bas niveau qui s’avèrent mal adaptées. Nous voudrions leur fournir des langages proposant un niveau d’abstraction plus élevé de façon à rendre la conception plus facile.”

Quant aux nouvelles architectures qui vont naître de ces recherches, “elles seront proposées en open hardware. C’est une tendance forte dans notre domaine et nous souhaitons contribuer à ce mouvement.”

|