Les rayons cosmiques peuvent perturber le fonctionnement du matériel électronique embarqué dans les avions, les engins spatiaux et parfois même au sol. À l’initiative de la Direction générale de l’armement (DGA), le centre lnria Rennes – Bretagne Atlantique et l’Office national d’études et de recherches aérospatiales (Onera) se joignent à la PME grenobloise Temento Systems pour élaborer un flot de conception logiciel capable d’améliorer la tolérance aux fautes des processeurs multi-cœurs destinés aux applications critiques.

Émises par le soleil et les étoiles, des particules électriquement chargées bombardent en permanence la planète. L’atmosphère et le champ magnétique terrestre forment un bouclier contre ces radiations. Mais à mesure que l’on s’approche des pôles ou que l’on monte en altitude, la protection faiblit. Quand l’une de ces particules traverse un matériau semi-conducteur, elle y dépose au passage quelques électrons. Conséquences ? “Cela peut impacter le fonctionnement des portes logiques et des mémoires, résume Olivier Sentieys, responsable de Cairn (1) une équipe Inria spécialisée dans l’architecture des systèmes sur puces. La sortie de la porte risque de passer de 0 à 1 ou l’inverse pendant un court instant. On appelle cela une erreur transitoire qui va se propager dans le circuit. Maintenant, si la particule traverse un bit mémoire, celui-ci peut changer d’état et rester verrouillé jusqu’à ce qu’on le réécrive.”

Des transistors de moins de 50 atomes

Pour limiter ces dysfonctionnements, l’aéronautique et le domaine spatial utilisent des composants électroniques durcis. Revers de la médaille : les processeurs de dernière génération font rarement partie du voyage. “Les semi-conducteurs avancés sont tellement miniaturisés et fonctionnent sous des tensions d’alimentation tellement faibles que l’impact des radiations devient de plus en plus sensible. Un transistor de dernière génération comporte moins de 50 atomes, donc une particule va plus facilement le perturber.”

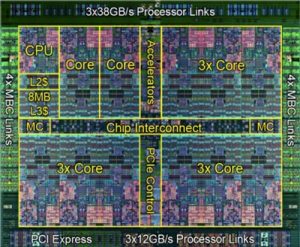

Parmi les grands absents figurent en particulier les processeurs multi-cœurs. “Les avionneurs préfèrent souvent installer plusieurs monoprocesseurs durcis et reliés par des câbles” indique la chercheuse Angeliki Kritikakou. “Il coûterait évidemment moins cher de mettre tout cela sur un seul circuit ou sur un composant reconfigurable de type FPGA, ajoute Olivier Sentieys. Mais pour l’instant les industriels n’ont pas confiance.” Cela dit, une tendance s’amorce : “dans les années à venir, les constructeurs commenceront à utiliser des composants standard et multi-cœurs pour des applications critiques. Il faut donc développer des techniques tant en architecture qu’en logiciel pour garantir la tolérance aux fautes.”

Comment ? “Il existe de multiples techniques pour cela. Nous allons produire une méthodologie pour les explorer et, en fonction des paramètres fournis par l’Onera, proposer certaines plus que d’autres. On peut imaginer par exemple de refaire trois fois le même calcul dans le temps. Si le résultat est trois fois le même, alors on peut garantir l’exactitude du calcul. On appelle cela de la redondance temporelle. Mais on peut aussi opter pour de la redondance matérielle et décider d’exécuter le calcul sur trois cœurs différents ou d’encoder les données et les calculs.” C’est là qu’intervient la société Temento Systems en fournissant des outils de vérification d’architecture multi-cœurs qui vont nous permettre de valider rapidement nos techniques de durcissement. Ces mêmes outils permettront également de tester par injection de stimuli sur plateforme FPGA la tolérance aux fautes des conceptions que nous aurons préalablement durcis.

Mettre en lien les physiciens et les architectes de processeurs

“Nous allons étudier ces stratégies pour trouver les plus prometteuses, mais d’un autre côté, il faut aussi éviter d’augmenter les coûts de calcul, explique Angeliki Kritikakou. Une partie du défi consiste à trouver le bon équilibre. Cela va dépendre également des contraintes des différentes applications et des modèles physiques fournis par l’Onera. L’un des intérêts de ce projet est d’ailleurs de mettre en lien des physiciens et des architectes de processeurs.”

“Ce sont des mondes qui ne se connaissent pas, confirme Olivier Sentieys. L’idée de la DGA de vouloir les rapprocher est très pertinente. Les physiciens vont avoir des applications à leurs modèles théoriques. Quant à nous, les architectes, nous allons travailler à partir de modèles de fautes plus réalistes.”

Toutes ces expériences seront menées sur un prototype virtuel qui simule une architecture multi-cœur. “En l’occurrence, nous avons choisi d’utiliser le processeur RISC-V, dont le jeu d’instructions lancé par l’université de Berkeley est libre de droits et que l’on peut déjà considérer comme l’équivalent de Linux au processeur. Son utilisation se répand aussi actuellement dans l’industrie.”

| (1) Située à Lannion et Rennes, Cairn est une équipe-projet Inria Rennes – Bretagne Atlantique, École normale supérieure de Rennes, CNRS, Université Rennes 1, commune à l’IRISA (UMR6074).

Crédit photo : Designed by Image par |